# White Paper 4 Understanding Electrical Overstress - EOS

# **Industry Council on ESD Target Levels**

# August 2016

Revision 1.2

This document is available through various public domains as listed below:

The Industry Council on ESD <a href="http://www.esdindustrycouncil.org/ic/en/">http://www.esdindustrycouncil.org/ic/en/</a>

The Electrostatic Discharge Association http://www.esda.org/

JEDEC – Under Publication JEP174 http://www.jedec.org/

#### **Abstract**

Damage signatures from Electrical Overstress (EOS) are the leading reported cause of returns in integrated circuits and systems that have failed during operation. Solutions to this problem are hindered by a prevailing misconception in the electronics industry that insufficient robustness to electrostatic discharge (ESD) is a primary cause of EOS. This document, White Paper 4, (WP) has been carefully compiled by the Industry Council on ESD Target Levels to foster a unified global understanding of what constitutes EOS and how EOS damage signatures can result from a wide variety of root causes.

The paper begins by outlining a brief history of EOS. It then presents the results of an industry-wide EOS survey. This survey gathered information on the types of EOS problems experienced by over 80 different companies, the relative importance of EOS to their overall business, and the methods assigned by these companies to address EOS issues. The survey provides a combined picture from which a more comprehensive definition of EOS can be made. The numerous categories and subcategories of EOS root causes are explored in an attempt to understand how to create better specifications which will reduce their occurrence. In addition to the survey results, this paper studies many field returns with EOS damage signatures to establish the underlying root causes of damage and offers the respective identified solutions.

The survey and the case studies both show that successful failure analysis (FA) depends on careful communication between customer and supplier from the time a failure occurs until its cause has been discovered. Detailed investigation into manufacturing and handling processes is often necessary to accurately identify the root cause. This paper outlines a basic summery of the typical process flow for component electrical failure analysis.

The key point is that EOS issues can be mitigated when the proper understanding of IC design, factory and field environments, and system implementation is combined with effective communication across all these areas.

#### Purpose

This purpose of this white paper will be introduce a new perspective about EOS to the electronics industry. As failures exhibiting EOS damage are commonly experienced in the industry, and these severe overstress events are a factor in the damage of many products, the intent of the white paper is to clarify what EOS really is and how it can be mitigated once it is properly comprehended. It is very clear that EOS is predominantly a matter of what customers do with devices, and in which applications the semiconductor specifications are exceeded causing destruction of the device. This white paper will describe those phenomena and explain the most important facts so that the involved partners in the industry have the opportunity to understand and recognize helpful steps for analysis and avoidance of EOS events.

In view of the above, we define EOS in terms of its impact inside applications. We focus on exceedance of specifications but not on how an exact specification was originally created. We focus instead on when and how the specifications are exceeded to cause EOS damage.

It is intended that this document be disseminated throughout the semiconductor industry for the benefit of those persons whose positions are concerned with the real nature of EOS. It is intended to serve as a foundational reference document for existing and future technologies.

#### **Additional Motivation**

A key finding from the Council's investigation is that component level ESD specifications and robustness have at most a minimal role in leading to an EOS condition or causing returns that exhibit EOS damage. While relating ESD scenarios to EOS, the document explicitly emphasizes the non-correlation between EOS return rates and Component ESD Target Levels. This is fully in line with what has been established in the Industry Council's white papers published as JEDEC documents JEP155 and JEP157.

#### **About the Industry Council on ESD Target Levels**

The Council was formed in 2006 after several major U.S., European, and Asian semiconductor companies joined to determine and recommend ESD target levels. The Council now consists of representatives from active full member companies and numerous associate members from various support companies. The total membership represents IC suppliers, contract manufacturers (CMs), electronic system manufacturers, original equipment manufacturers (OEMs), ESD tester manufacturers, ESD consultants and ESD intellectual property (IP) companies.

| Core Contributing Members                                                      | Core Contributing Members                      |  |

|--------------------------------------------------------------------------------|------------------------------------------------|--|

| Robert Ashton, ON Semiconductor                                                | Masaki Tanaka, Renesas Technology              |  |

| Fred Bahrenburg, Dell                                                          | Christoph Thienel, Bosch                       |  |

| Patrice Besse, Freescale                                                       | Benjamin Van Camp, SOFICS                      |  |

| Brett Carn, Intel Corporation                                                  | Vesselin Vassilev, Novoroll                    |  |

| Ann Concannon, Texas Instruments                                               | Jim Vinson, Intersil                           |  |

| Jeff Dunnihoo, Pragma Design                                                   | Scott Ward, Texas Instruments                  |  |

| Charvaka Duvvury, Texas Instruments - Retired (Chairman)<br>cduvvury@gmail.com | Terry Welsher, Dangelmayer Associates          |  |

| David Eppes, AMD                                                               | Joost Willemen, Infineon Technologies          |  |

| Reinhold Gärtner, Infineon Technologies                                        |                                                |  |

| Robert Gauthier, IBM                                                           |                                                |  |

| Harald Gossner, Intel Corporation (Chairman)<br>harald.gossner@intel.com       | Advisory Board                                 |  |

| LeoG Henry, ESD/TLP Consulting                                                 | Agha Jahanzeb, Apple                           |  |

| Satoshi Isofuku, Tokyo Electronics Trading                                     | Heiko Dudek, Cadence                           |  |

| John Kinnear, IBM                                                              | Stephen Frei, Technical University of Dortmund |  |

| David Klein, Synaptics                                                         | Ludger Kappius, Hella                          |  |

| Hans Kunz, Texas Instruments                                                   | Frederic Lefon, Valeo                          |  |

| Timothy Maloney, Intel Corporation                                             | Christian Lippert, Audi                        |  |

| Tom Meuse, Thermo Fisher Scientific                                            | Amit Abhay Mohabey, Tata Motors                |  |

| James Miller, Freescale Semiconductor                                          | Joseph Ney, GM                                 |  |

| Guido Notermans, NXP Semiconductors                                            | Patrice Pelissou, EADS                         |  |

| Mototsugu Okushima, Renesas                                                    | Wolfgang Pfaff, Bosch                          |  |

| David Pommereneke, Missouri University of Science & Technology                 | James Roberts, Continental                     |  |

| M K Radhakrishnan, NanoRel Technical Consultants                               | Marc Sevoz, EADS                               |  |

| Wolfgang Reinprecht, AustriaMicroSystems                                       | Stephen Sibrel, Harman                         |  |

| Alan Righter, Analog Devices                                                   | Werner Storbeck, Volkswagen                    |  |

| Theo Smedes, NXP Semiconductors                                                | John Timms, Continental                        |  |

| Teruo Suzuki, Socionet                                                         | Wolfgang Wilkening, Bosch                      |  |

| Pasi Tamminen, Microsoft Corporation                                           | Rick Wong, Cisco                               |  |

|                                                                                |                                                |  |

|                                                                                |                                                |  |

|                                                                                |                                                |  |

| Associate Members                            | Associate Members                                    |  |

|----------------------------------------------|------------------------------------------------------|--|

| Jon Barth, Barth Electronics                 | Han-Gu Kim, Samsung                                  |  |

| Stephen Beebe, Global Foundries              | Marcus Koh, Everfeed                                 |  |

| Jonathan Brodsky, Texas Instruments          | Soon-Jae Kwon, Samsung                               |  |

| Michael Chaine, Micron Technology            | Brian Langley , ORACLE                               |  |

| Freon Chen, VIA Technologies                 | Frederic Lafon, Valeo                                |  |

| Ted Dangelmayer, Dangelmayer Associates      | Moon Lee, SemTech                                    |  |

| Ramon del Carmen, Amkor                      | Markus Mergens, QPX                                  |  |

| Tom Diep, Texas Instruments                  | Nate Peachey, Qorvo                                  |  |

| Stephanie Dournelle, ST Microelectronics     | Roger Peirce, Simco                                  |  |

| Melanie Etherton, Freescale Semiconductor    | Ghery Pettit, retired IEEE EMC Society               |  |

| Yasuhiro Fukuda, OKI Engineering             | Jeff Salisbury, Flextronics                          |  |

| Howard Gan, SMIC                             | Jay Skolnik, Skolnik-Tech                            |  |

| Horst Gieser, FhG IZM                        | Jeremy Smallwood, Electrostatic Solutions Inc.       |  |

| Mike Heaney, Amazon                          | Jeremy Smith, Silicon Labs                           |  |

| Masamitsu Honda, Impulse Physics Laboratory  | Arnold Steinman, Electronics Workshop                |  |

| Michael Hopkins, Amber Precision Instruments | David E. Swenson, Affinity Static Control Consulting |  |

| Kelvin Hsueh, UMC                            | Nobuyuki Wakai, Toshiba                              |  |

| Natarajan Mahadeva Iyer, Global Foundries    | Gene Worley, Qualcomm                                |  |

| Larry Johnson, LSI Corporation               | Jon Williamson, IDT                                  |  |

| Marty Johnson, Texas Instruments             | Michael Wu, TSMC                                     |  |

| Peter de Jong, Synopsys                      | MyoungJu.Yu, Amkor                                   |  |

| Jae-Hyok Ko, Samsung                         |                                                      |  |

| ChangSu Kim, Samsung                         |                                                      |  |

#### **Acknowledgments:**

#### **Editors:**

Brett Carn, Intel Corporation Hanna Klein

#### **Authors:**

Robert Ashton, ON Semiconductor Fred Bahrenberg, Dell Jeff Dunnihoo, Pragma Design Charvaka Duvvury, Texas Instruments (Retired) David Eppes, AMD Reinhold Gärtner, Infineon Technologies Harald Gossner, Intel Mobile Communications Leo G Henry, ESD/TLP Consulting John Kinnear, IBM David Klein, Synaptics Hans Kunz, Texas Instruments Jean-Luc Lefebvre, Presto Tim Maloney, Intel Corporation Jim Miller, Freescale Semiconductor M K Radhakrishnan, NanoRel Technical Consultants Alan Righter, Analog Devices Theo Smedes, NXP Semiconductors Pasi Tamminen, Microsoft Corporation Christoph Thienel, Bosch Jim Vinson, Intersil Terry Welsher, Dangelmayer Associates

The Industry Council would like to extend their heartfelt thanks to the ESD Association for their support in arranging meeting space for the Industry Council during the ESDA's regularly scheduled ESDA events.

#### **Mission Statement**

The Industry Council on ESD Target Levels was founded to review the ESD robustness requirements of modern IC products in order to allow safe handling and mounting in an ESD protected area. While accommodating both the capability of the manufacturing sites and the constraints posed by advanced process technologies on practical protection designs, the Council provides a consolidated recommendation for future ESD target levels as well as guidelines for various EOS and ESD topics. The Council Members and Associates promote these recommended targets and guidelines for adoption as company goals. Being an independent institution, the Council presents the results and supportive data to all interested standardization bodies.

#### **Preface**

This white paper has been written with the intent to provide a comprehensive understanding of what EOS is and is not, the importance of EOS to the industry, and what optimum measures can be taken to mitigate EOS damage to ICs, as well as products and systems. The wealth of material contained in this document should provide the industry with some often overlooked information as well as establish the notion that EOS is a complex phenomenon which requires thorough understanding on both the supplier side and the OEM side. This document should prove valuable to OEM and IC quality organizations, IC designers, failure analysis (FA) engineers, test engineers, customer interface, and system engineers. Our goal is that through this document more attention will be focused on properly addressing the often preventable failures exhibiting EOS damage. The chapters are organized to give as many technical details as possible to support the purpose explained in the abstract. The paper begins with an Executive Summary giving a high level message and ends with a list of frequently asked questions (FAQ) so that the reader can readily find critical information. These FAQs are intended to clear up misconceptions that commonly occur while interpreting EOS data.

## **Scope**

The scope of this white paper is damage to integrated circuits and systems caused by electrical stress, the terms and definitions associated with electrical stress to these integrated circuits and systems and the mitigation of this electrical stress event as it applies to integrated circuits and systems.

#### **Disclaimers**

The Industry Council on ESD Target Levels is not affiliated with any standardization body and is not a working group associated with JEDEC, ESDA, JEITA, IEC, or AEC.

This document was compiled by recognized ESD experts from numerous semiconductor supplier companies, contract manufacturers and OEMs. The data represents information collected for the specific analysis presented here; no specific components or systems are identified.

The Industry Council, as well as the member organizations, while providing this information, do not assume any liability or obligations.

# **Table of Contents**

|          | nd Definitions                                                                                         |     |

|----------|--------------------------------------------------------------------------------------------------------|-----|

|          | ons                                                                                                    |     |

| Executiv | ve Summary                                                                                             | 14  |

| Chapter  | 1: History of EOS                                                                                      |     |

| 1.0      | General Introduction to Historical References                                                          | 22  |

| 1.1      | Outline of History of Relevant Professional Societies                                                  | 23  |

| 1.2      | EOS – A Brief History                                                                                  | 24  |

| 1.3      | Transition to Present                                                                                  |     |

| Chapter  | 2: EOS Damage in the Factory and Field                                                                 | 31  |

| 2.0      | Outline                                                                                                |     |

| 2.1      | Motivation for Field Returns Analysis of Failures Exhibiting EOS Damage                                | 31  |

| 2.2      | Transients                                                                                             |     |

| 2.3      | EOS Survey for Gathering Data on EOS Damage                                                            | 33  |

| 2.4      | Impact of EOS Damage                                                                                   |     |

| 2.5      | Failure Reports of Products Exhibiting EOS Damage                                                      | 51  |

| Chapter  | 3: The Definition of EOS – Finding Common Understanding                                                | 52  |

| 3.0      | Introduction                                                                                           |     |

| 3.1      | Existing Documentation Practices of AMR Values                                                         |     |

| 3.2      | Unified Understanding of AMR and EOS                                                                   |     |

| 3.3      | Additional Comments on Usage of the Term "EOS"                                                         | 56  |

| 3.4      | Conclusion                                                                                             |     |

| Chapter  | 4: EOS Root Causes                                                                                     | 58  |

| 4.0      | Purpose                                                                                                | 58  |

| 4.1      | Root Cause Categories                                                                                  | 58  |

| 4.2      | EOS Damage during Unpowered Handling                                                                   | 59  |

| 4.3      | EOS during Powered Handling                                                                            |     |

| 4.4      | EOS Damage during AC Operation and Switching                                                           | 68  |

| 4.5      | Analysis of Electrically Induced Physical Damage and Conclusions on EOS Events                         | 68  |

| Chapter  | 5: Case Studies on EOS                                                                                 | 72  |

| 5.0      | Introduction                                                                                           | 72  |

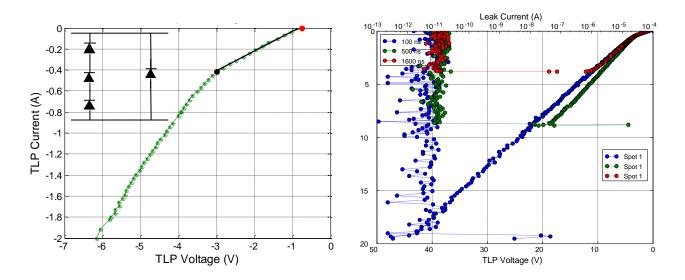

| 5.1      | Case 1: Incorrect ESD Qualification Leading to EOS.                                                    | 74  |

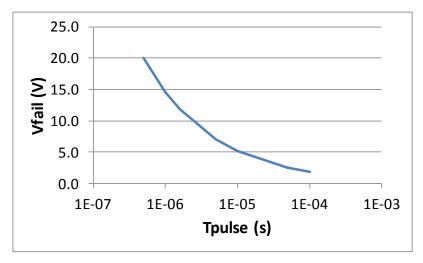

| 5.2      | Case 2: EOS Due to Misapplication                                                                      | 76  |

| 5.3      | Case 3: EOS due to Hot Plugging                                                                        | 79  |

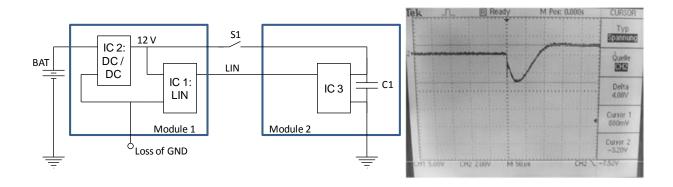

| 5.4      | Case 4: EOS due to Intermittent Battery Ground Connection                                              | 83  |

| 5.5      | Case 5: EOS due to Ground Offset                                                                       | 86  |

| 5.6      | Case 6: EOS Case Study "Automotive Knock Sensor"                                                       | 88  |

| 5.7      | Case 7: EMI – Transient Surge                                                                          | 93  |

| 5.8      | Case 8: EMI – Board Design                                                                             | 96  |

| 5.9      | Case 9: Supply Capacitor Switching                                                                     | 99  |

| 5.10     | Case 10: CBE in DSP IC                                                                                 | 102 |

| 5.11     | Case 11: Reliability Testing                                                                           | 108 |

| 5.12     | Lessons Learned                                                                                        | 111 |

| 5.13     | Conclusions                                                                                            | 112 |

| Chapter  | 6: EOS Analysis and Diagnosis - "Techniques and Methods for Dealing with Electrically Induced Physical |     |

| Damage   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                | 114 |

| 6.0      | Introduction                                                                                           |     |

| 6.1      | Optimal Customer and Supplier Failure Symptom Information Exchange and Device Handling                 | 114 |

| 6.2      | EOS FA Challenges                                                                                      | 115 |

| 6.3      | High Level Preparation Guidelines for Diagnosing the Cause of EOS                                      |     |

| 6.4      | Failure Analysis Techniques and Procedures                                                             | 117 |

| 6.5      | Analysis of Damage Mechanisms for EOS                                                                  |     |

| 6.6      | Overstress Power vs. Time                                                                              |     |

| 6.7      | Final Diagnosis of the Cause and Conclusion                                                            |     |

| Chapter  | 7: Minimization and Mitigation of EOS                                                                  |     |

| -        | Introduction                                                                                           |     |

| 7.1     | Lessons Learned to Minimize EOS Damage                          |     |

|---------|-----------------------------------------------------------------|-----|

| 7.2     | Automotive Studies                                              | 143 |

| 7.3     | Integrated Circuit Trends and EOS Effects                       |     |

| 7.4     | Communication with Customers                                    | 161 |

| 7.5     | Recommendations for EOS Minimization and Mitigation             |     |

| 7.6     | Conclusions                                                     |     |

|         | 8: Summary and Conclusions                                      |     |

| Append  | ix A: EOS Survey Form                                           |     |

| Append  | ix B: The Dwyer Curve and EOS Damage at a Temperature Threshold | 175 |

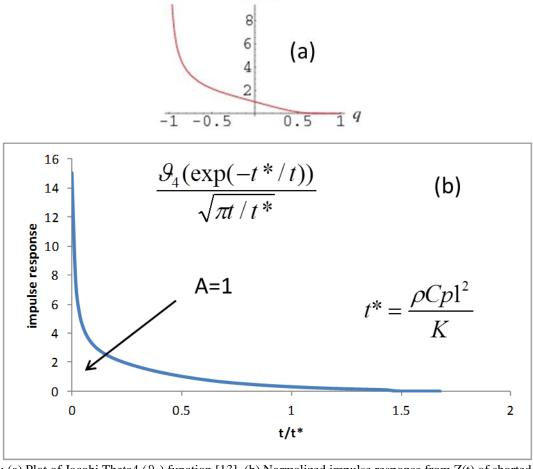

| B.0     | Background and 1-Dimensional Heat Flow                          | 175 |

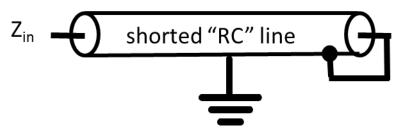

| B.1     | Heat Flow as an RC Transmission Line                            |     |

| B.2     | Thermal Impedance and the Jacobi Theta4 Function                | 177 |

| B.3     | The Analytic Dwyer Curve Approximation                          |     |

| B.4     | Utility of the Dwyer Curve and Thermal Impedance Approximations |     |

|         | ix C: Frequently Asked Questions                                |     |

| Revisio | n History                                                       |     |

|         |                                                                 |     |

#### **Terms and Definitions**

AC alternating current A/D analog/digital

AEC Automotive Electronics Council

AlCu Aluminum Copper

AMR absolute maximum rating

ANSI American National Standards Institute

ASIC application specific integrated circuit

ATE automated test equipment

ATPG automatic test program generation

BIST built-in self-test

BJT bipolar junction transistor BTI bias temperature instability

BVii injection induced breakdown voltage

CAN controller area network

CBE charged board event

CBM charged board model

CDE cable discharge event

CDM charged device model

CMOS complimentary metal-oxide-semiconductor

CM contract manufacturer

DC direct current

DMOS double-diffused metal-oxide-semiconductor

DSP digital signal processing/processor DRAM dynamic random access memory

DUT device under test

ECU electronic control unit

ECL emitter-coupled logic

EDX energy dispersive X-ray

EIPD electrically induced physical damage

EMC electromagnetic compatibility EMI electromagnetic interference

EMP electromagnetic pulse

EOS electrical overstress

ES electrical stress

ESD electrostatic discharge

ESDA Electrostatic Discharge Association; ESD Association

ESDS electrostatic discharge sensitive

ESREF European Symposium on Reliability and Failure Analysis

FA failure analysis

FAQ frequently asked question FEM finite element model FFR failed failure rate FIB focused ion beam

FICDM field induced charged device model FICBE field induced charged board event

FIT failure-in-time

FMLB first-mate-last-break

GND negative voltage supply in digital logic, neutral voltage supply in analog

logic

HBM human body model HCI hot carrier injection HMM human metal model

HTOL high temperature operating life

IC integrated circuit ICT in-circuit test IO input/output

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

IPFA International Symposium on the Physical and Failure Analysis of Integrated

Circuits

IRPS International Reliability Physics Symposium

ISTFA International Symposium for Testing and Failure Analysis

ISO International Organization of Standards

I-V current/voltage

JEDEC JEDEC Solid State Technology Association (formerly Joint Electronic

**Device Engineering Council)**

JEITA Japan Electronics and Information Technology Industries Association

JTAG joint test action group LC inductor capacitor

LCT liquid crystal thermography

LIN local interconnect network

LIVA light-induced voltage alteration

LSM laser scanning microscopy

LU latch-up

MCU microprocessor control unit

MM machine model

MOS metal-oxide-semiconductor

MOSFET metal-oxide-semiconductor field-effect transistor

NBTI negative biased temperature instability

NiCr nickel-chromium

NMOS N-channel metal-oxide-semiconductor

NPN negative-positive-negative (transistor)

OBIRCH optical beam induced resistance change

OEM original equipment manufacturer

PBL powered bipolar latching

PCB printed circuit board

PCBA printed circuit board assembly

PMOS P-channel metal-oxide-semiconductor PNP positive-negative-positive (transistor)

PPM parts per million

PQFP plastic quad flat pack

RC resistor capacitor network

RF radio frequency

SCR semiconductor controlled rectifier; silicon controlled rectifier

SEM scanning electron microscopy

SMD surface mount device SOA safe operating area SoC system-on-chip STM standard test method

TC timing circuit

TDDB time dependent dielectric breakdown

TDR time domain reflectometry

TEM transmission electron microscopy

TIVA thermally induced voltage alteration

TLP transmission line pulse

TTL transistor-transistor logic

TVS transient voltage suppression

USB universal serial bus VDD positive voltage supply

VFTLP very fast transmission line pulse

VLSI very large scale integration

VSS negative voltage supply

VSWR voltage standing wave ratio

W-B Wunsch-Bell WP white paper

#### **Definitions**

electromagnetic interference (EMI): Electromagnetic emissions (radiated or conducted) which may cause harmful interference to communications services or other electronic devices.

<u>ESD</u> design window: The ESD protection design space for meeting a specific ESD target level while maintaining the required IO performance parameters (such as leakage, capacitance, noise, etc.) at each subsequent advanced technology node.

second-breakdown trigger current  $-(I_{12})$ : The amount of current at the point in time when a transistor enters its second-breakdown region under ESD pulse conditions and is irreversibly damaged

#### **Executive Summary**

In this summary the Industry Council will address the most important electrical overstress (EOS) issues and conclusions of White Paper 4. Further details can be found in the various chapters of the document.

#### **Traditional Perceptions of EOS**

Through the years, a high incidence of failures exhibiting EOS damage has been reported in most market segments of electronics and related industries, such as the automotive industry. This damage has often been mislabeled as "EOS Failure", implying that these malfunctions are solely a result of a phenomenon or stress called EOS. Understanding EOS as a "stress" has led many customers to incorrectly assume a device experiencing EOS is "weak". This misperception has led to requests to "improve" a device in regards to EOS.

Another incorrect assumption has been that EOS can be avoided by making devices more ESD robust to both the human body model (HBM) and the charged device model (CDM). This misconception has been addressed in JEDEC publications JEP155 [1] and JEP157 [2] where it is convincingly shown that the incidence of EOS is independent of the level of HBM and CDM robustness.

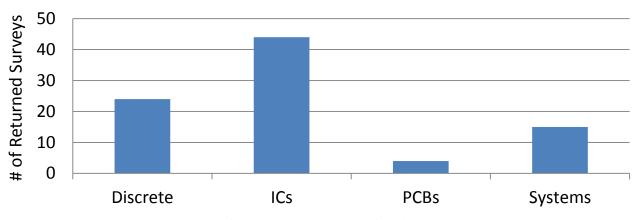

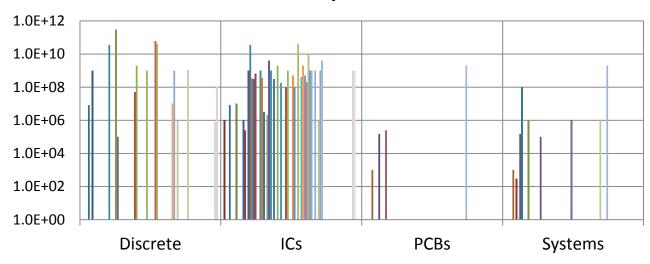

#### **Industry Council Worldwide Survey**

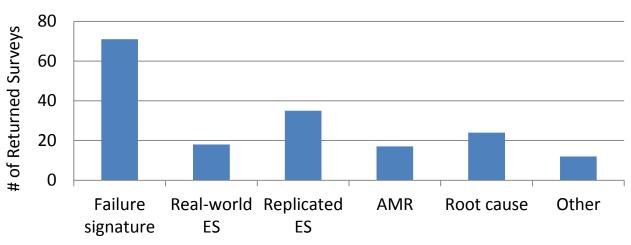

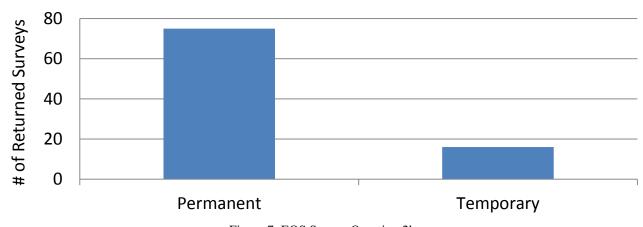

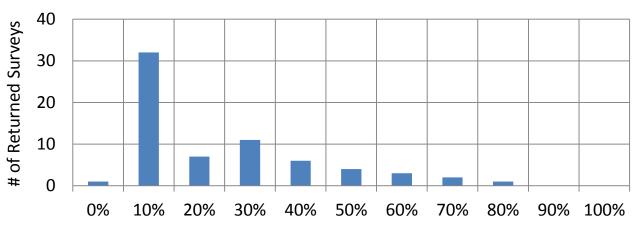

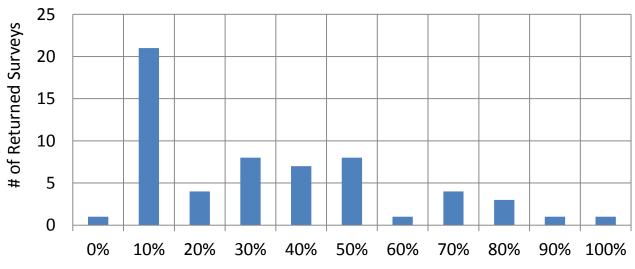

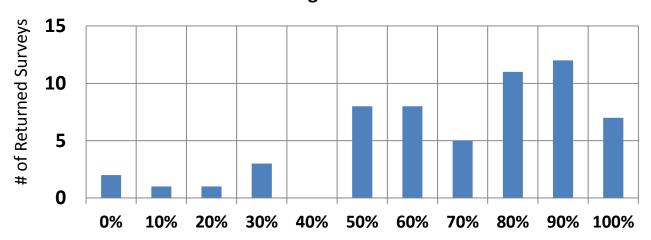

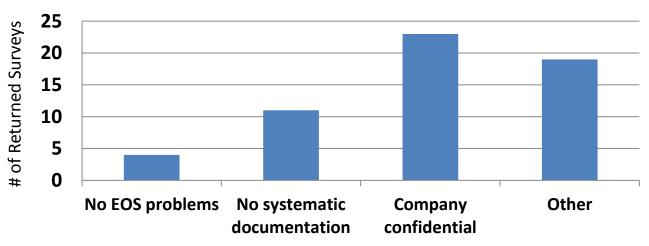

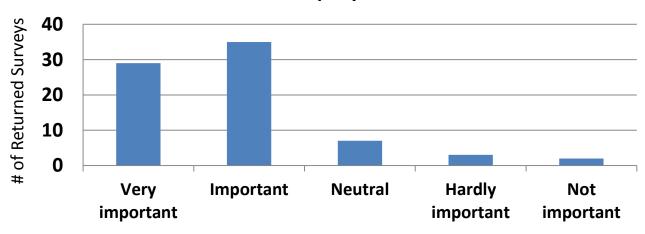

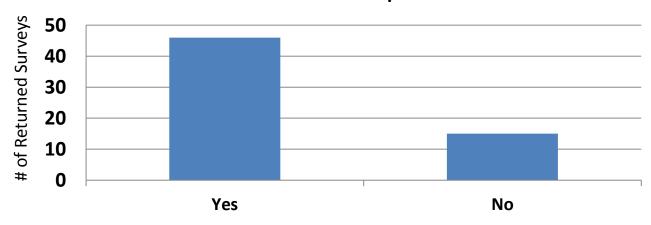

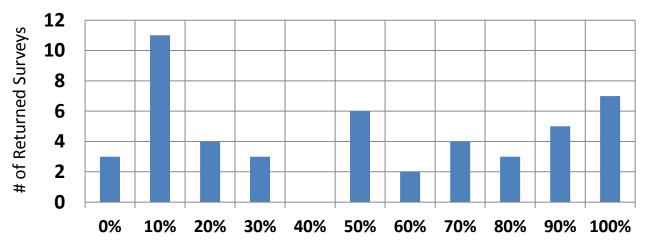

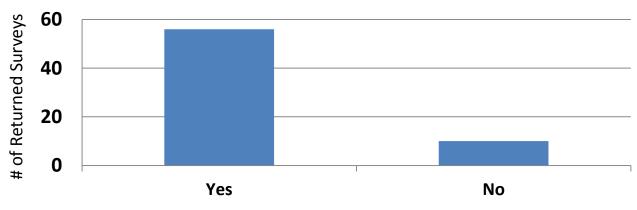

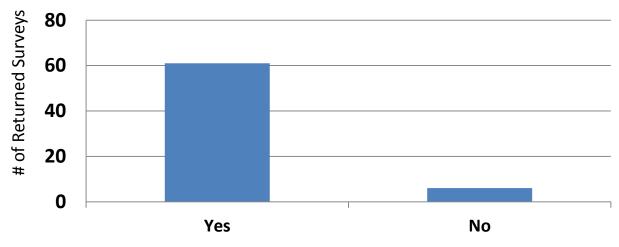

In preparation for this white paper, the Industry Council conducted a worldwide survey of the electronics industry concerning EOS. Results confirmed the long held view that EOS is consistently one of the "high bars" on product failure Pareto charts. Looking at the EOS survey, respondents reported greater than 20% of total failures being EOS-related or 30% of total electrical failures being EOS-related, making EOS the largest bar on the Pareto chart of that responder's known causes of returns. One glaring revelation was the critical need for a better industry-wide understanding of EOS to address its issues.

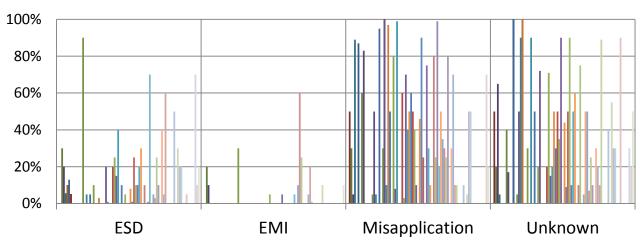

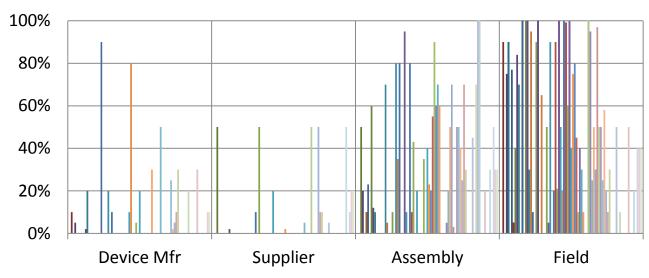

Looking at the EOS survey further, misapplication (powered handling) stands out as the highest cause of EOS damage, with over 40% of respondents indicating EOS damage which occurred in the field as the most common location. Damage signatures associated with EOS often can involve package and silicon damage and are more extensive in a product than failure signatures resulting from events in the measurable ESD regimes. The main findings of the EOS Survey were:

- 1. **Powered Handling**: This stands out as the most widely reported root cause, involving a significant (over 20%) percentage of reported returns exhibiting EOS damage. Powered handling can include overvoltage, improper insertion, power supply sequencing, and incorrect biasing during use.

- 2. **Absolute Maximum Rating (AMR):** A number of returns exhibiting EOS damage were attributed to applied voltages exceeding the specified AMR voltage, indicating that incomplete or unclear maximum ratings may be an issue and that AMR characterization and improved AMR information on the datasheets is important to minimize the risk of EOS.

- 3. **ESD Related**: System level events, discharges from charged devices, and ESD controls in manufacturing which are not compliant with handling ESDS devices are additional root

causes for EOS damage. Charged board events (CBE) and cable discharge events (CDE) also contribute.

4. **Miscellaneous Causes**: There were other miscellaneous causes reported that ranged from weak printed circuit board (PCB) designs to mishandling.

#### New Definition of EOS Incorporating AMR and EIPD

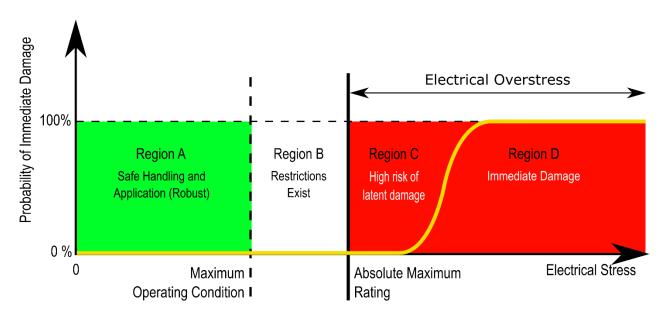

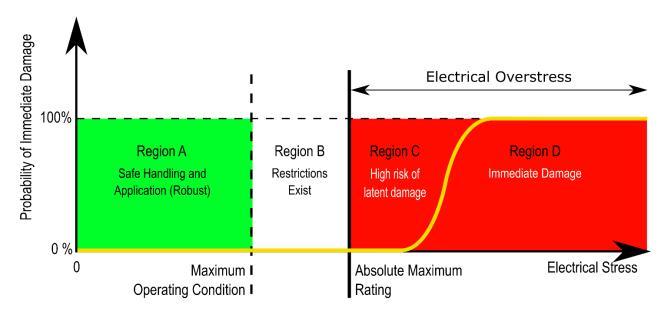

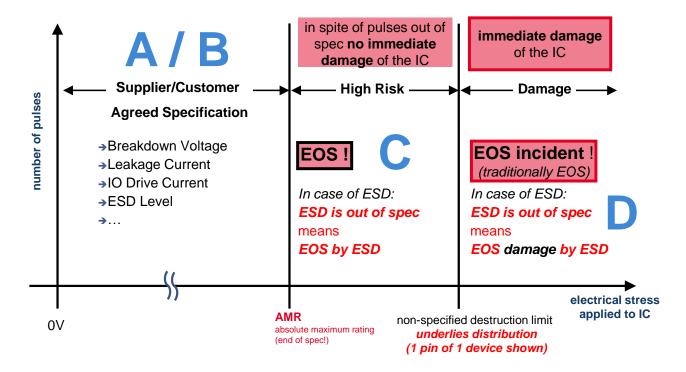

It became clear to the Council during analysis of the survey, as well as gathering data on customer—supplier experiences with resolving EOS-related returns that a new way of visualizing the relationship of AMR to EOS is sorely needed in the industry. The Council proposes that the relationship between EOS and AMR may be illustrated in the manner indicated in Figure 1. Definition of AMR and its relationship to device stress, reliability impact and long and short term damage potential allows semiconductor manufacturers to clearly provide the maximum voltage / current / power limits. This enables system manufacturers to incorporate devices into their systems safely and ensure an operational environment that does not exceed those maximum limits. This is based on the following EOS definition:

An electrical device suffers an electrical overstress event when a maximum limit for either the voltage across, the current through, or power dissipated in the device is exceeded and causes immediate damage or malfunction, or latent damage resulting in an unpredictable reduction of its lifetime.

Critical to this definition is a clear understanding of what is meant by maximum limit. Chapter 3 further expands this definition by providing a practical interpretation of EOS in terms of AMR. Insight into the electrical aspects of AMR can be gained by examining the voltage ranges illustrated in Figure 1.

Figure 1: A graphical depiction of how Absolute Maximum Ratings should be interpreted. The yellow line is the number of components suffering immediate, catastrophic EOS damage

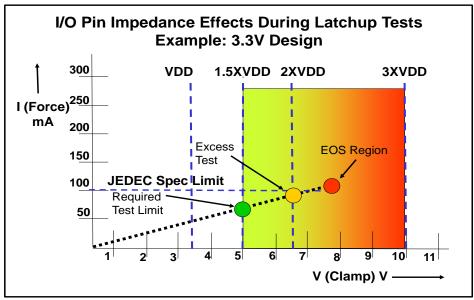

First, there is the safe operating area, a region of robust operation (region A). This is the region in which the manufacturer designed the device to operate. This is followed by a region in which operating restrictions exist (region B). In region B, the device is not guaranteed to function as specified, however the device is not expected to be physically damaged. Operating the device in region B for extended periods of time may also result in reliability issues. The upper limit of region B is the AMR. At and beyond the AMR the user should expect problems. Beyond the AMR are two regions of *electrical overstress* with either latent (region C) or immediate (region D) damage as a result of exceeding AMR. Note that the transition between latent damage and immediate damage is subject to normal process variations as illustrated by the yellow S curve. In order to properly evaluate the product reliability and robustness, it is important to understand that some qualification stresses, such as device level ESD and latch-up, are *expected* to run evaluations that will exceed AMR. For example, in the case of latch-up, this may be necessary in order to get significant current injection to assess latch-up robustness.

There are different methods a device manufacturer may use to determine AMR values. The manufacturer may pick very conservative AMR values not based on physical properties of the product. This results in a wide region C before the onset of immediate damage. Alternatively, the manufacturer may define the AMR values based on detailed circuit and technology understanding resulting in a more accurate prediction of the damage threshold. This can result in the near elimination of region C. Regardless of the method chosen, the manufacturer is solely responsible for defining the AMR. Further, an AMR is a function of stress duration and any single documented value will have a fixed time association. Consequently, a clear understanding of the AMR by a system manufacturer is necessary to ensure that the operating environment of the system is within the specified conditions and that the limits defined in the AMR are never exceeded. This is particularly important when the system is using the semiconductor device in new or unique configurations. In these special cases, communication between the supplier and system manufacturer is absolutely necessary, particularly if the AMR does not appear to cover a mode of operation the system manufacturer expects their system to experience.

Beyond this discussion of regions of operation where the AMR describes maximum electrical and environmental values of operation, there is controversy about whether it should also refer to ESD limits. As noted above, while recognizing that this definition of EOS focuses attention on the AMR, placing greater significance and expectations on its limits than may have been given in the past, each supplier has their own approach to setting the AMR values. With respect to ESD, several different approaches have been observed:

- Some suppliers do not include ESD limits as part of their AMR because testing to establish the ESD limits often does not have similar statistical data collected as is required for setting more traditional items such as voltage.

- Some suppliers do place ESD limits in their AMR definition as it is felt that this is part of the overall agreement that must be met between supplier and customer.

- Other suppliers have placed ESD limits in an AMR section did so for no other reason than it was the only place that it made sense to them.

Regardless of the approach taken, the supplier is *solely* responsible for deciding what parameters and limits are included in their product's AMR. Since this discussion on AMR could be a new interpretation of existing documentation, system manufacturers should be communicating with their

suppliers to verify that AMR information for any datasheet published prior to release of this white paper has appropriate meaning and that system manufacturers do not misinterpret the information as having a different meaning than the supplier originally intended.

This white paper also points out that failure analysis engineers are likely to assign, albeit some would say prematurely, the term EOS to any visible damage signature that appears to have been the result of excessive voltage or current. These assignments are often based on experience and may often be correct. However, after initial failure analysis, often times it is unclear as to whether a device has experienced EOS per this white paper's definition until further communication between supplier and customer has been carried out. The damage could be a violation of an AMR caused by incorrect biasing in the application, over voltage, induced latch-up conditions, extreme uncontrolled ESD, misorientation, or something else entirely. The damage may also have been due to a defect in an individual weak device, an improperly set AMR or an intrinsic weakness in the technology. To that extent, this white paper introduces the term "electrically induced physical damage" (EIPD) to represent the term that should be used by FA engineers when no clear communication has been completed with the customer as to possible root causes of the damage. The definition of EIPD is the following:

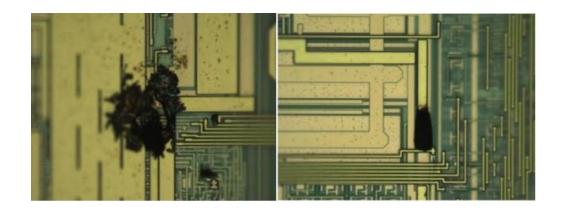

Damage to an integrated circuit due to electrical/thermal stress beyond the level which the materials could sustain. This would include melting of silicon, fusing of metal interconnects, thermal damage to package material, fusing of bond wires and other damage caused by excess current or voltage.

The term EIPD is used when it has not yet been determined if a unit experienced an EOS event by the definition of EOS above and elaborated on in Chapter 3. That conclusion can only be determined after the supplier and customer have worked together to arrive at potential root causes.

#### **EOS Root Causes**

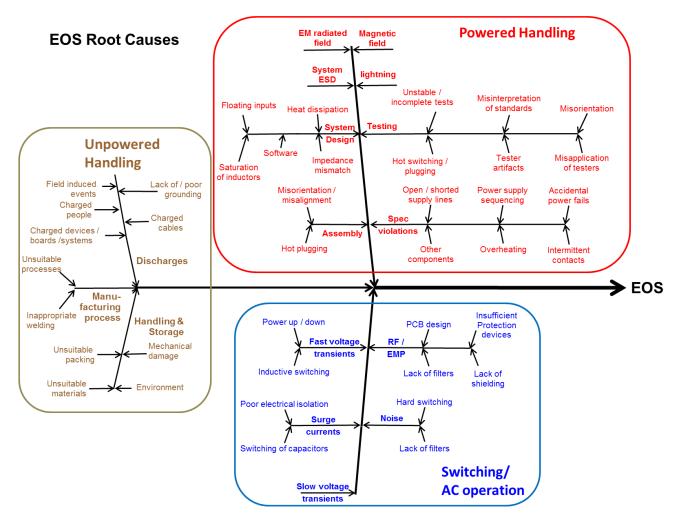

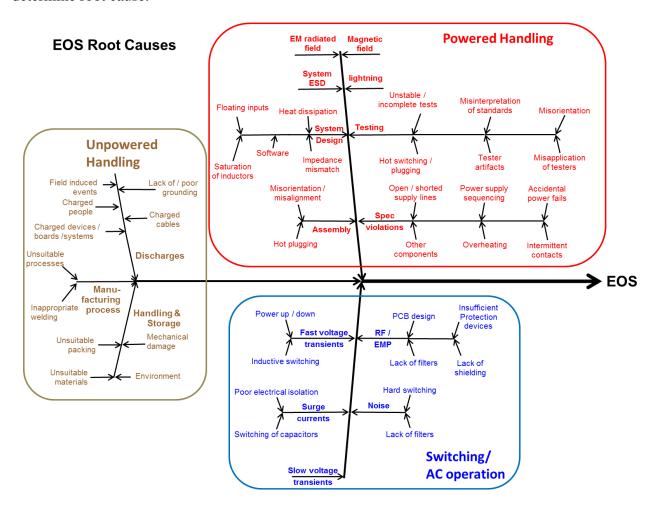

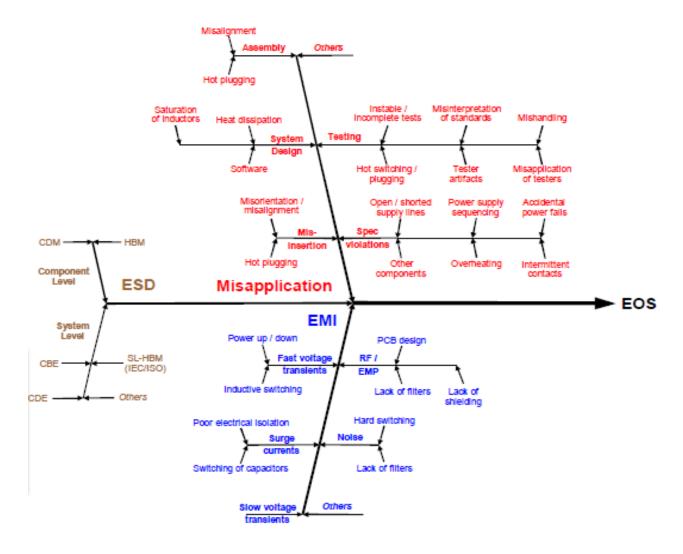

As shown in the fishbone diagram of Figure 2, there are many categories and sub-categories for EOS root causes. The three main categories where EOS damage can occur are:

- 1) powered handling

- 2) unpowered handling

- 3) switching / alternating current (AC) applications

Each category can be traced to a specific sub-category shown as branches in the fishbone diagram of Figure 2. The sub-categories of Figure 2 are not meant to be an exhaustive list of root causes but an overview of some of the more common root causes.

Figure 2: Fishbone Diagram Representing Different Root Causes Leading to EOS

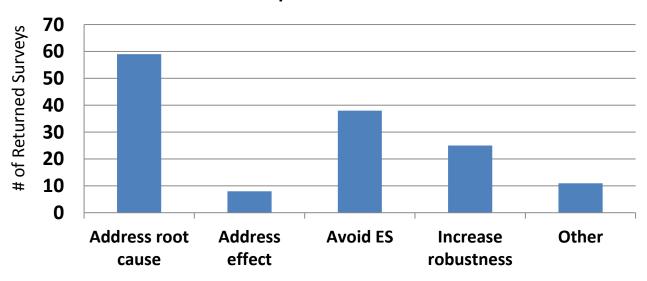

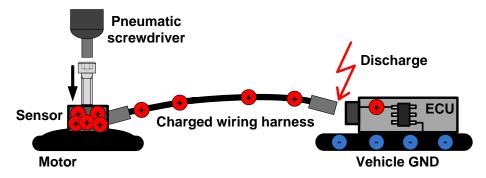

Based on the EOS survey, the most common cause of EOS events is powered handling. Events may be related, for example, to overstress-induced phenomena when power is turned on, incorrect power supply sequencing, electromagnetic interference (EMI), or hot plugging. In addition, there are many system ESD events, especially during specification testing, which may result in unintended EOS damage. For responders showing a higher confidence level of finding a root cause of EOS damage (70 % to 100 %), a majority of those responders most often reported root causes which included hot plugging, overshoot / overvoltage, power surge, and misorientation being in their top 3, see Table 1 in Chapter 2. Clearly powered handling is an area where more focus is needed to address EOS damage.

In the unpowered branch, possible root causes include: an external charged source discharging into or through the device; the charged device/system being discharged; or the device/system being in an electrostatic field when the discharge has occurred. It should be noted that the root causes in unpowered handling are ESD-like in nature but may not be specifically related to the HBM or CDM testing performed as part of a product qualification. In fact, as the survey responses suggest, ESD represents a very small percentage of what constitutes EOS damage. Many manufacturers spend significant time auditing factories for ESD, thinking this will resolve all EOS events, when in

actuality, it will only address a small percentage of EOS related damage. Auditing a factory for EOS involves a much more in-depth look at power delivery systems and connection issues with significant focus on the powered handling root causes shown in Figure 2.

Typical root cause examples in the category of switching / AC operation are radio frequency (RF) coupling, spurious electromagnetic pulses (EMP) or poor PCB design, all of which may result in EOS damage. This category had the lowest reported incidence as root causes of EOS damage but this could be a result of the difficulty in properly assessing the environment for this category.

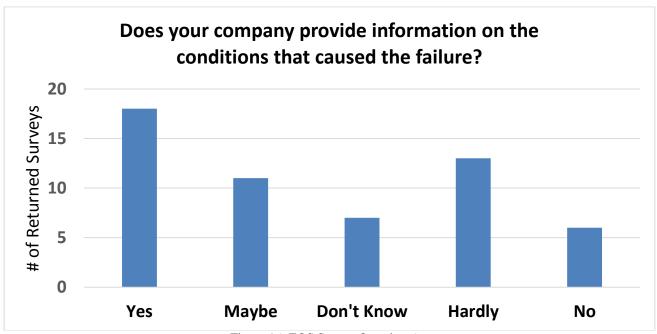

#### **EOS Root Cause Diagnostics**

When failed products are returned, proper failure analysis (FA) methods become crucial, but the success in determining root cause depends on the process flow used in this work. Communication and cooperation between customer and supplier must happen if the root cause is to be found. One challenge involves determining what can be classified as EOS and what should not be considered as EOS. The analysis itself can be lengthy as failure analysis times can range from days to months. Chapter 6 discusses the factors that play a critical role in the analysis time. The analysis can also be complex, involving tools from optical microscopy to acoustic microscopy to assess the component and many other advanced techniques including analysis of the system board characteristics. But this may only identify a *cause*. Coupling the device failure analysis with the product return signature and the use environment is critical to finding the root cause. While proper training and the tools available to FA engineers described in this paper are necessary, an FA engineer can only find the cause of the device damage (such as the identification of the damage signature and probable polarity / path of transients resulting in the damage), not the root cause of what created the EOS event as shown in Figure 2. Therefore, there must be a cooperative effort between supplier and customer to find the root cause. It should be noted that in some cases, such as in a singular damaged unit or if the use environment in which the damage occurred is unknown, it may not be possible to determine root cause.

#### **EOS Case Studies and IC Designs**

There are many EOS damage scenarios that can be avoided if the product field return causes are understood. White Paper 4 discusses these in detail and establishes some important conclusions on A) **Product EOS Returns**, B) **IC Technology / Design Issues**, and C) **Field and Factory Events**.

- A) Case studies of product returns with EOS damage signatures were analyzed to determine a root cause. This allowed a reduction of EOS occurrences and demonstrated how appropriate solutions can be identified to meet customer needs. Some important conclusions are:

- 1. Failure analysis only provides a damage signature and probable path and does not reveal the true root cause.

- 2. Incorrect testing limits during qualification can lead to failures being falsely identified as EOS.

- 3. An EOS damage signature could be due to a broad list of root causes including, but not limited to; hot-plugging, ground bounces, supply switching, EMI transient surges, and process / product / system assembly issues.

- B) Technology scaling and IC protection designs can also have some impact on EOS returns. A summary of these investigations reveal:

- 1. Today's advanced process technologies have not shown any obvious increase in return rates for products exhibiting EOS damage when compared to older, more robust technologies [1, 2]. It should be cautioned that further technology advances, with thinner gate dielectrics and novel transistor process technologies, will reduce breakdown voltages and continue to shrink design windows. This reduction in breakdown voltage will reduce AMRs and may subsequently begin to influence returns which exhibit EOS damage. In all cases, it will become even more critical to adhere to the AMR boundaries and maintain clear communication between supplier and customer.

- 2. As previously established, lowering ESD target levels for compatibility with technology scaling and circuit performance have no impact on EOS return rates.

- 3. However, IC ESD protection design styles and implementations can have an impact on EOS if careful adherence to AMR values is not addressed. A summary of the design styles and their impacts are summarized in Chapter 7.

- C) Factory and field return analysis can provide lessons learned as listed below:

- 1. EOS damage can occur due to poor grounding methods and can easily be mitigated with established guidelines. A risk analysis often can avoid such problems.

- 2. Learning from field events is important. Many of the problems could be avoided if the supplier and the board designer communicate early in the product application development cycle having knowledge of possible root causes.

- 3. Automotive applications pose some of the most common risks. For example, hot plugging is a persistent problem in automotive electronics interconnection that can be mitigated by practicing the principle of first-mate-last-break.

- 4. EOS caused by ESD can be reduced by avoiding charging/discharging in manufacturing lines and implementing a balanced ESD protection approach.

#### **EOS Mitigation and Communication**

An important focus of this white paper is to convey the proper understanding of EOS, fostering communication between supplier and customer and reducing the number of returns exhibiting EOS damage in the industry. Useful customer communication methods are identified based on observed case studies and the expected influences from IC designs, production issues, field events, and application issues. Points to consider include:

- 1) Proper understanding of AMR

- 2) Realistic specifications of AMR and customer realization of its limits

- 3) Accurate determination of the location and possible causes of the damage and finding the true root cause event which created the damage

- 4) Understanding the use application and impacts to the IC's ESD protection design

- 5) Lessons learned from product returns from both manufacturing and the field

These are summarized to help the industry deal with returns exhibiting EOS damage.

#### **Summary**

This is the first known comprehensive document on EOS in electronics manufacturing and operations written to foster understanding of EOS, root cause determination for resolving EOS issues, and implementation of methods for EOS mitigation. A common language on EOS as documented here is the first significant step to help solve and mitigate EOS issues. IC suppliers, customers, applications engineers, and system builders alike should take part in understanding and solving EOS. Finally, customers and suppliers should treat all conditions for applications as a contract and agree that all unspecified conditions are not allowed. Education of these important aspects is the responsibility of all parties involved.

#### Outlook

For over four decades, EOS has been one of the top causes of returns for semiconductor devices and systems. The Industry Council has documented here an extensive study which enhances understanding of EOS and recommends many approaches to reduce EOS damage. This should be of great value in preventing EOS from becoming a catastrophic issue in the next generation of technologies involving even more consumer, medical, military, and automotive applications. It would be important to revisit the information presented here at a later date and conduct another industry wide survey to see how much impact this work has made. EOS *is* inherent in the application of electronic systems. Only through continuous learning and sharing of experiences can future risks be avoided.

#### References

- [1] Industry Council on ESD Target Levels, "White Paper 1: A Case for Lowering Component Level HBM/MM ESD Specifications and Requirements," August 2007, at <a href="http://www.esda.org/IndustryCouncil.html">http://www.esda.org/IndustryCouncil.html</a> or JEDEC publication JEP155, "Recommended ESD Target Levels for HBM/MM Qualification", www.jedec.org

- [2] Industry Council on ESD Target Levels. "White Paper 2: A Case for Lowering Component Level CDM ESD Specifications and Requirements," Revision 2, April 2010, at <a href="http://www.esda.org/IndustryCouncil.html">http://www.esda.org/IndustryCouncil.html</a> or JEDEC publication JEP157, "Recommended ESD-CDM Target Levels", <a href="https://www.jedec.org">www.jedec.org</a>

#### **Chapter 1: History of EOS**

Leo G. Henry, ESD/TLP Consulting

Jeff Dunnihoo, Pragma Design

M K Radhakrishnan, NanoRel Technical Consultants

Jim Vinson, Intersil

Terry Welsher, Dangelmayer Associates

#### 1.0 General Introduction to Historical References

In the 19<sup>th</sup> century, one of the first widespread applications of electro-mechanical systems with a well-known vulnerability to electrical overstress was the telegraph system. During storms, operators purposely ceased operations for fear of direct and indirect lightning strikes which could burn stations, melt wires and equipment and kill operators [1].

With the proliferation of vacuum tube communication equipment in the early 20<sup>th</sup> century, more complex component and system failure modes presented themselves. With the novelty of electronics in consumer applications, thermal and power supply robustness design issues competed with operator error and user repair problems. This formed the familiar basis for modern overload and overstress phenomenon.

Early radio repair (and kit construction) manuals of the 1920's and 30's included troubleshooting guides for finding melted grids and burned filaments on tubes, as well as procedures for determining failed open or shorted passive components when the hobbyist did not have even a voltmeter for debug.

The etymology of the term overstress implies a limit which is exceeded. This is synonymous with the term overload which was more generally used at the time to refer to any functional or permanent deviance from intended operation. Consider the following definitions from the Modern Dictionary of Electronics (1962) [2]:

OVERLOAD - 1. A load greater than that which an amplifier, other component, or a whole transmission system is designed to carry. It is characterized by waveform distortion or overheating. 2. In electronics, it is that quantity of power from an amplifier or other component or from a whole transmission system which is sufficient to produce unwanted waveform distortion.

OVERLOAD CAPACITY - The level of current, voltage, or power beyond which a device will be ruined. It is usually higher than the rated load capacity.

OVERLOAD LEVEL - The level at which a system, component, etc., ceases to operate satisfactorily and produces signal distortion, overheating, damage, etc.

At first glance, these would seem to be distinct from EOS, in that they pertain more to temporary functional failures or performance degradations. However, these passages elegantly define the resulting observations which are indicative of having exceeded maximum component limits. If we

consider a burned filament in a tube, or a shorted P-N junction in an integrated circuit, we can assume that the device will forever fail to perform with acceptable operational functionality.

Partial damage, such as a semiconductor with leakage, might be detected by signal distortion of a reference test pulse or level, overheating under normal loads, or visible physical damage. Thus the concept of permanent damage due to EOS can be found in the early definitions of overload which may or may not have created permanent damage, depending on the performance requirements.

Absolute maximum ratings (AMR) first appeared routinely in solid state datasheets in the late 1960's and early 70's. These limits are due to the unique process technologies of early emitter-coupled logic (ECL), transistor-transistor logic (TTL), and N-channel metal-oxide-semiconductor (NMOS) which alerted the designers to power supply and interface level limits at a time when signaling voltages and polarities were not strictly defined and constrained by unique interface designs (such as RS-232, IEEE-488, etc.)

Generally, while input signals could cause problems in some circuitry, AMR's tended to convey a guarantee by the component supplier that if the thermal and voltage envelope limits were not exceeded, the component would never be permanently damaged or degraded and would remain completely within all other electrical performance specifications.

Exceeding the AMR for any period of time did not guarantee permanent damage, and indeed the ratings were often very conservative or "sandbagged" with wide guard bands because it was often difficult for designers to accurately gauge the robustness limits of a new technology.

#### 1.1 Outline of History of Relevant Professional Societies

This historical note by Colvin [3] covers the origin of many EOS related professional societies:

"Published papers for Failure Analysis date back to 1954 for the Annual Symposium on Reliability and back to 1963 for the International Reliability Physics Symposium (IRPS). Another familiar resource to the failure analyst in the USA is the Symposium for Testing and Failure Analysis (ISTFA). ISTFA proceedings were originally known as ATFA (Advanced Techniques in Failure Analysis) and date back to 1974. The Microelectronic Failure Analysis Desk Reference (1996-2012) is an important companion to the ISTFA Workshops. IPFA (International Symposium on the Physical and Failure Analysis of Integrated Circuits) is another resource of information. The conference for IPFA has been held annually in Singapore for the last 6 years (ED NOTE: since 1987). ESREF is a European forum for reliability of electron devices, failure physics and analysis. ESREF held its first symposium in 1990. The annual EOS/ESD Symposium started in 1979 in the US. One of the goals being to elevate the awareness to the destructive nature of EOS and ESD to electronic components. Additional resources of information are the Journal of Electrostatics, an Elsevier publication, ESA (Electrostatics Society of America), and IEJ (Institute of Electrostatics Japan)".

#### 1.2 EOS – A Brief History

Two of the earliest researchers were Wunsch-Bell [4], who did not mention EOS by name but whose physical modeling implied a path to melting at high temperatures for semiconductor components. The time dependent Wunsch-Bell equation generally defined as  $P/A = f(t^x)$  also shows that the power per unit junction area varies with pulse width, and is actually a thermal diffusion equation which depends on thermal conductivity and the product of density and specific heat. This model characterizes a component's failure power threshold versus an input pulse duration (time dependent pulse width). A plot of the device behavior shows 3 regions: a short pulse width (<0.1  $\mu$ s) ESD region, a longer pulse width (0.01 – 20  $\mu$ s) Wunsch-Bell region, and a very long pulse width (> 20  $\mu$ s) flat region. This is the region which leads to melting, because the thermal conductivity and the density-specific heat product are both temperature dependent properties of the semiconductor material, and so this flat pulse width region is directly related to EOS type failures, as a result of high heating with time in addition to pulse width.

Additionally, some early mentions of the word overstress appears to be in 1971 [5], when Smith and Shumka were analyzing complimentary metal-oxide-semiconductor (CMOS) microcircuits and silicon devices. They reported that up to 29 % failed due to external overstress; unfortunately a detailed FA of these failures was not included. In 1979 [6], Rutherford and several others reported on the electrical overstress of digital bipolar microcircuits and silicon devices claiming that 60-75 % were EOS damage. Some used charged capacitors (up to 0.01  $\mu$ F) as the input stress. Lee [7] attempted to interpret the EOS damage in power transistors and semiconductors. Melted bond wires, fused or alloyed metallization all fell under the category of EOS damage.

From 1983 to 1985, several authors, Lee [8], Middendorf [9], and May [10] reported the EOS damage from power circuits to power transistors. They used the terms *melted metal*, *dissolved metal*, *melt-through* and *burnt metal* in their description for EOS damage, but there was no mention of the bond wires. The use of the combined terms EOS/ESD is significant, where the combined term is used to mean EOS and/or ESD, i.e. EOS alone, ESD alone or both if the diagnosis is uncertain. However, the authors pointed out that the use of the shorter duration pulse distinguished between the ESD damage and the longer pulse EOS damage, in most cases.

In 1988 [11], Lee conducted simulation and characterization of EOS damage in metal-oxide-semiconductor field effect transistor (MOSFET) transistors and ICs by capacitive discharge. Here, Lee used much larger capacitors (200  $\mu F$  to 4500  $\mu F$ ) to dump more energy into the device. Lee reported that the large metal melt-through also obliterated the ESD protection circuits. The wire bonds were also damaged. Using the lower capacitance (up to 200 pF) resulted instead in ESD damage between the source and drain in the ESD circuits. Hence, differentiating between EOS and ESD damage was of primary importance early on.

In 1989, Richardson Jr. [12] described an overvoltage stress test in TTL electronics, which resulted in melted metal, open metallization, melted input transistors, and damaged input protection diodes. A curve tracer was used as the voltage simulator, and all voltages were greater than the rated maximum voltages for the TTLs. The failures were referred to as electrical damage. The same year, Kiefer [13] studied the damage in high-speed CMOS gate arrays using the machine model (MM) as the simulator (in order to produce more power) and referring to the process as an EOS stress. This resulted in the usual fused/melted metal, all damage being visible with a low magnification microscope. At lower machine model (MM) voltages, the damage was not immediately visible, but

on removal of topside glass/oxide and the metal below, the damage could be seen in the oxide below the drain-to-source contacts. These were referred to as ESD melt filaments failures. These authors simulated an EOS stress after first ESD stressing the devices. They called this an "ESD/EOS" stress, meaning ESD stress followed by an EOS stress. The damage seen was fused metal plus protrusions of poly-silicon melt filaments in the contacts, and also between the contacts. These authors were attempting to show the difference between EOS damage and ESD damage.

Also in 1989, two authors (Willis [14] and Kitamura [15]) discussed locating EOS/ESD failures without explaining why they used the combined terms (EOS/ESD). They reported the following long list of failures: damaged/degraded junctions, blown open and punched through contacts, ruptured dielectrics, gate oxide pin holes, gate edge pinholes, aluminum melting, fused open aluminum metal, thermal damage of diffusion resistors, and melted silicon. They only used two electrical stress types, HBM and transmission line pulse (TLP), and labeled some figures EOS, and some ESD, with no clear discussion or clarification as to which failure belongs to the two different stresses.

Launer [16] related discoloration to EOS damage in 1990 when he presented EOS damage data after electrically overstressing passivated nickel-chromium (NiCr) resistors using two different pulse sources (a HBM 150 ns pulse width and a 200 ns to 120 µs square pulse). He referred to HBM as an alternating current (AC) source of adiabatic EOS, resulting in discolored NiCr resistors because there was no significant heat beyond the oxide. He referred to the square pulse as a direct current (DC) source with its long pulse width, which also caused EOS damage (including the discoloration) in the NiCr resistors. No explanation was given in the report as to why these two different events resulted in the same EOS type damage.

May, [17] in the same year (1990), presented and discussed the EOS discoloration concept, but applied it to the metallization using pulse widths of 10  $\mu$ s, 120  $\mu$ s, through to DC. The author concluded that the lateral thermal diffusivity occurs in the metallization, and therefore across the whole device.

Between 1991 and 1994, several authors, Wilson [18], Schani [19], Glacet [20], and Henry [21] demonstrated that EOS damage could be produced from either negative/positive step stress pulses, overvoltage/overcurrent stressing, from IC life test, and IC burn-in attributing one mechanism to the process-induced metal stress relief during the IC life test and/or burn-in test. This EOS simulation allowed the authors to speculate as to how to differentiate between EOS and ESD type damage. Then, in 1998, Henry and Mazur [22] in their paper "Basic Physics in Color-Coded EOS Failures" were able to do just that by applying some physics principles to the process. The visible EOS damage was the same as that seen by earlier authors: die surface burnt, fused metal, etc.

Most of the previously mentioned authors reported that EOS damage was optically visible at very low magnification - open metallization, fused metal, burnt/discolored metal, melted metal, fused open metal, package distortion/blistering, and melted sockets (on the board). One author used the non-destructive acoustic microscopy method to externally view the EOS damage inside the package. The package compound was shown to be thermally degraded. It showed internal delamination (die interface-die attach), voids, the aluminum wires were fused or burnt and had molding compound on them, die cracks, burnt/carbonized plastic, and package cracks under the die pad. They also reported the electrical signatures as shorts, opens, high leakage, and high resistance.

In 1995, Lisenker [23], working on a CMOS very large scale integration (VLSI) product, used the combined term ESD/EOS to mean ESD stress, followed by EOS stress to simulate the observed failures. He suggested that the metal burn-out occurred after the gate oxide punch-through (or juncture failure) occurred, creating a short which drew enough current in a powered device to melt the metal stripe. Hence the use of the combined term ESD/EOS. He used burn-in, a process of operating the device under certain electrical and thermal stress conditions which accelerates the life of the device and removes poor quality devices. Several other authors in the same year [24], 1995, showed EOS damage in insulated-gate bipolar transistor modules (each module contained several devices). The damage included burnt wires, melted wires, melting pits in bond pads, and melted material penetrated deep in the silicon chip. They used a square pulse frequency test (high voltage 50 Hz -12 kHz cycles 600 V-1300 V) through a charging capacitor and inductor.

In 1997, Milburn & Parekh [25] reported that the EOS damage (melted/open metal) was precipitated by excessive voltage or power generating a high current over a period of time, and in 1998 Vinson [26] studied the aluminum interconnect response to EOS, calling EOS the stress, instead of the failure, and reporting that EOS is the event causing the failure, and the aluminum film responded to the EOS event. They concluded that Joule heating caused failure as a result of excessive currents due to overvoltage from a power surge, inductive kickback from an inductive load, or application of a voltage to an output pin in the nanosecond to second range. They provided the following definition of EOS: "a class of failure from an applied stimulus condition exceeding the normal operation of the circuit". Yet some authors referred to the failure as aluminum EOS, or EOS damage or EOS of aluminum lines—all interchangeably.

In 2001, Wang [27] described EOS damage as a result of over-current or over-voltage events ranging from microseconds to milliseconds. The author reported that EOS causes uncontrollable overheating (thermally induced failures) which leads to electromigration failure, intermetallic compound formation, and delamination on die surface. Vinson [28] also saw EOS damage, but the cause of the EOS was an excessive electrical stimulus (V or I) applied to the unit resulting in the damage. EOS then is an event that occurs at a point in time, triggering the failure. It is not a wearout mechanism that degrades with time, but the failure is quite visible, and in some cases the metal from the contact migrates into the silicon shorting out the junction (damaged junction).

In 2003, Korchnoy [29] showed that the silicon substrate and diffusion layers can be affected by ESD in such a way that the damage extends up though the interlayer dielectric to the metallization causing it to melt both at the contacts and the metallization because of the excessive current flow. He called these ESD/EOS failures, i.e. ESD induced EOS damage.

#### 1.3 Transition to Present

In the period between the earliest, most elementary electrical circuitry overloads and the more recent academic and industrial analysis, the body of knowledge, terms and definitions have grown dramatically. EOS damage has been categorized by early researchers based on the physical results to try to determine the type of event, energy content, and duration of the event to help identify the source. Papers defining a method to characterize devices for EOS robustness were not always present. Also, most did not include physical modeling of EOS in the semiconductor devices, but there were some papers which attempted to describe how to improve the safe operating area (SOA)

of transistors, SOA refers to the maximum voltage and current that a transistor can sustain without damage under specific conditions.

While the mechanisms may be related or even identical, often the definitions and terms used coherently within the scope of one paper or author may be confusing or even conflicting when compared to other sources. As Alfred Korzybski observed, it is important in any semantic system to index and date the terms used whenever the same word may be mapped by different authors and readers to different meanings at different times. The underlying physics of the phenomena may remain timeless and universal, but the labeling and classification may have been inconsistent.

The balance of this document investigates these issues in more detail and tries to add clarity to the use of the terms and definitions, aided with the benefit of the historical literature amassed so far.

#### References

- [1] Modern practice of the electric telegraph: A handbook for electricians and operators. By Franklin Leonard Pope, 1868

- [2] MODERN DICTIONARY OF ELECTRONICS 3rd Ed. by Rudolf F. Graf 1962-1970

- [3] Jim Colvin, "ESD failure analysis methodology", Microelectronics Reliability, Volume 38, Issue 11, November 1998, pp. 1705–1714

- [4] D.C. Wunsch and R.R. Bell, "Determination of Threshold Failure Levels of Semiconductor Diodes and Transistors due to Pulse Voltages", IEEE Trans. Nuc. Sci., NS-15, pp. 244-259, 1968.

- [5] Smith & Shumka et al "A Laser Scanner for Solar Cell Evaluation and Failure Analysis", Advanced Techniques in Failure Analysis-1978

- [6] Rutherford, D.H, Perkins, J.F, "Effects of Electrical Overstress on Digital Bipolar Microcircuits and Analysis Techniques for Failure Site Location", EOS/ESD Symposium 1979, pp. 64

- [7] T. W. Lee, "Transient damage in Power Transistors" ISTFA, 1979, pp. 130

- [8] T. W. Lee, "The Interpretation of EOS Damage in Power Transistors" ISTFA, 1983, pp. 157

- [9] M.J. Middendorf et al, "Observed Physical Effects and FA of EOS/ESD Damage on MOS devices", ISTFA, 1984, pp. 205

- [10] J.T. May, "The interpretation of EOS Damage in Power Circuits", ISTFA, 1985, pp. 92

- [11] T.W. Lee et al, "Simulation and Characterization of EOS and ESD Damage in MOSFET Transistors and ICs by Capacitive Discharge" ISTFA, 1988, pp. 95

- [12] Z.C. Richardson Jr, "Failure Simulations allow Estimation of Overvoltage Condition in TTL Electronics", ISTFA, 1989, pp. 209

- [13] D.S. Kiefer et al, "ESD/EOS damage of HCMOS Gate Arrays", ISTFA, 1989, pp. 201

- [14] K.S. Willis, "Photoemission Testing for EOS/ESD Failures in VLSO Devices: Advantages and Limitations", ISTFA, 1989, pp. 183

- [15] Y. Kitamura et al, "Breakdown of Thin Gate Oxide by Application of Nanosecond Pulses", ISTFA, 1989, pp. 193

- [16] R.A. Launer et al, "Interpretation of EOS Damage in NiCr Resistors", ISTFA, 1990, pp. 279

- [17] J.T. May, "Interpretation of EOS-induced discoloration ICs", ISTFA, 1990, pp. 143

- [18] D. Wilson et al, "Interpretation of Severe EOS damage on Logic Circuitry", ISTFA, 1991, pp. 289

- [19] R. Schani et al, "A new IC Failure Mechanism due to Process-Induced Metal Stress Relief", ISTFA, 1992, pp. 413

- [20] J.Y. Glacet, "Identification of EOS Failures in semiconductor devices using acoustic microscopy" ISTFA, 1993, pp. 161

- [21] L.G. Henry et al, "Lab simulation and signature analysis of a CMOS programmable Logic Product", ISTFA, 1994, pp. 117

- [22] L.G. Henry, Mazur, "Basic Physics in Color-Coded EOS Failures", ISTFA, 1998, pp. 143

- [23] B. Lisenker et al, "Model of EOS Caused Electrical Failure Screening in CMOS VLSI", ISTFA, 1995, pp. 121

- [24] W. Wu et al, "EOS Failures in Power Insulated Gate Bipolar Transistor Modules", ISTFA, 1995, pp. 159

- [25] R. Milburn, K.H. Parekh, "Effectiveness of Emission Microscopy in the FA of CMOS ASIC Devices", ISTFA, 1997, pp. 299

- [26] J.E. Vinson, "Al interconnect response to EOS", ISTFA, 1998, pp. 103

- [27] Fan Wang et al, "IC failure by EOS", ISTFA, 2001, pp. 259

- [28] J. Vinson, "The Search for the elusive EOS", ISTFA, 2001, pp. 265

- [29] V. Korchnoy, "ESD Correlation between electrical signature and Failure modes", ISTFA, 2003, pp. 272

#### For Further Historical Reading

The following documents, while not explicitly referenced, have been included by the authors of this chapter as historically significant, relevant and instructive milestones in the evolution and advancement of the definition, characterization and analysis of electrical overstress.

#### **Most Recent**

- [30] K.T. Kaschani, Texas Instruments; "What is Electrical Overstress? Analysis and Conclusions"; Microelectronics Reliability Volume 55, Issue 6, May 2015, pp. 853–862

- [31] Alain Kamdem, Normandie Universite, Presto Engineering; Patrick Martin, Fanny Berthet, Bernadette Domengès, Dominique Lesenechal, Normandie Universite; Jean-Luc Lefebvre, Presto Engineering; Pierre Guillot, NXP Semiconductors, "Electrical Overstress Robustness and Test Method for ICs", EOS/ESD Symposium, 2014

- [32] Alan Righter, Ed Wolfe, Jean-Jacques Hajjar, Analog Devices, "Non-EOS Root Causes of EOS-Like Damage", EOS/ESD Symposium, 2014

- [33] T. Smedes, S. Zhao, NXP Semiconductors; Y. Christoforou, YC Industrial Projects (Formerly with NXP Semiconductors), "Characterization Methods to Replicate EOS Fails", EOS/ESD Symposium, 2014

- [34] Richard Wong, Shi-Jie Wen, Rita Fung, Paul Le, Cisco Systems Inc., "System Level EOS Case Studies not due to Excessive Voltages", EOS/ESD Symposium, 2013

- [35] KP Yan, Reinhold Gaertner, CY Wong, Infineon Technologies, "Poor Grounding Major Contributor to EOS", EOS/ESD Symposium, 2012

- [36] K.T. Kaschani, Texas Instruments; R. Gaertner, Infineon Technologies AG, "The Impact of Electrical Overstress on the Design, Handling, and Application of Integrated Circuits", EOS/ESD Symposium, 2011

- [37] Al Wallash, Hitachi Global Storage Technologies; Vladimir Kraz, BestESD Technical Services, "Measurement, Simulation and Reduction of EOS Damage by Electrical Fast Transients on AC Power", EOS/ESD Symposium, 2010

#### 2000's

- [38] Vladimir Kraz, 3M Company, "Origins of EOS in Manufacturing Environment and It's Classification", EOS/ESD Symposium, 2009

- [39] A. Wallash, H. Zhu, R. Torres, T. Hughbanks, Hitachi GST; V. Kraz, Credence Technologies, "A New Electrical Overstress (EOS) Test for Magnetic Recording Heads", EOS/ESD Symposium, 2006

- [40] I. E. T. Iben, IBM, "The Thermodynamics of Physical and Magnetic Changes to AMR Sensors from EOS at Variable Pulse Widths", EOS/ESD Symposium, 2005

- [41] W. Farwell, K. Hein, D. Ching, Raytheon Corporation, "EOS from Soldering Irons Connected to Faulty 120VAC Receptacles", EOS/ESD Symposium, 2005

- [42] C H Tung, etal., "Physical FA to Distinguish EOS & ESD Failures", IPFA 2002, pp. 65-69

- [43] M D Ker, JJ Peng & H C Jiang, "FA of ESD Damage in High Voltage Driver IC", IPFA2002, pp. 84

- [44] S Voldman, "ESD & FA Models, Methodology and Mechanisms", IPFA 2002, pp. 57-64

- [45] J C Reiner, etal., "Impact of ESD Induced Soft Drain Junction Damage", IPFA2001, pp. 77-78

- [46] Y. Jaimsomporn, S. Phunyapinuant, W. Tan, "Advanced Micro Devices, DC Transient Monitoring and Analysis to Prevent EOS in Burn-in Systems", EOS/ESD Symposium, 2001

- [47] E. Granstrom, R. Cermak, P. Tesarek, N. Tabat, "Seagate Recording Head Operations, Floating Gate EEPROM as EOS Indicators During Wafer-Level GMR Processing", EOS/ESD Symposium, 2000

#### 1990's

- [48] P S Lim & W K Chim, "Latent Damage Investigation on Lateral Non-Uniform Charge Generation and Stress-Induced Leakage Current in Silicon Dioxides Subjected to Low Level ESD Impulse Stressing", IPFA 1999, pp. 156-161

- [49] Banerjee, et al., "High Current Effects in Silicide Films for Sub-025um VLSI Technologies", IRPS, 1998

- [50] G. Baumgartner, J. Smith, Lockheed Martin, "EOS Analysis of Soldering Iron Tip Voltage", EOS/ESD Symposium, 1998

- [51] Vinson & Liou, "ESD in Semiconductor Devices: An Overview, Proceedings of the IEEE", 1998, pp. 399-418

- [52] Vinson, "Aluminum Interconnect Response to Electrical Overstress", ISTFA, 1998

- [53] Voldman, et al., "High Current Transmission Line Pulse Characterization of Aluminum and Copper Interconnects for Advanced CMOS Semiconductor Technologies", IRPS, 1998.

- [54] G L Teh & W K Chim, "Pre-Breakdown Charge Trapping in ESD Stressed Thin MOS Gate Oxide", IPFA 1997, pp. 156-161

- [55] McAteer, "Pulse Evaluation of Integrated circuit Metallization as an Alternative to SEM", IRPS, 1997, pp. 217-224.

- [56] T N Tang, C Francis & S T Teh, "ESD Failure Fingerprint in Devices", IPFA 1997, pp. 115-120

- [57] T S Yeah, "ESD Effects in Power Supply Clamps", IPFA 1997, pp. 121-124

- [58] W Tan, K K Goh & D Corum, "EOS Induced Transistor Shift in Submicron DRAMs", IPFA 1997, pp. 196-201

- [59] Banerjee, et al., "Characterization of VLSI Circuit Interconnect Heating and Failure under ESD Conditions", IRPS, 1996, pp. 237-245

- [60] K. Banerjee, et al., "Thermal Analysis of the Fusion Limits of Metal Interconnect Under Short Duration Current", International Reliability Workshop Final Report Proceedings, Oct. 1996, pp. 98-102

- [61] Ramaswamy, S., Li, E., Rosenbaum, E., Kang, S., University of Illinois at Urbana-Champaign, "Circuit-Level Simulation of CDM-ESD and EOS in Submicron MOS Devices", EOS/ESD Symposium, 1996

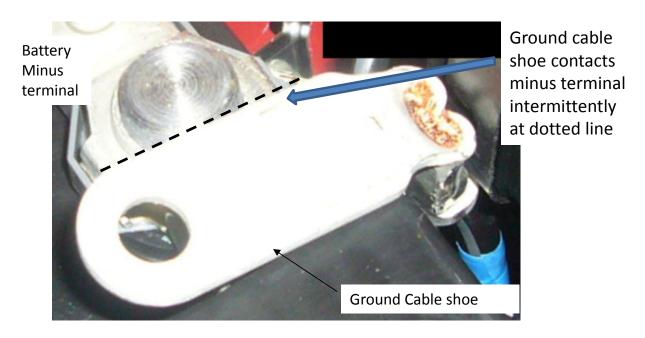

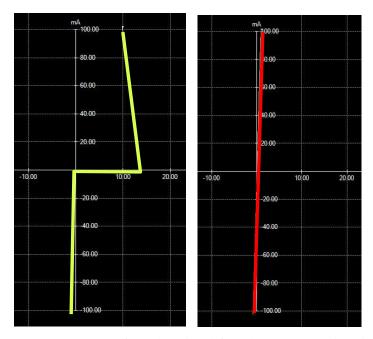

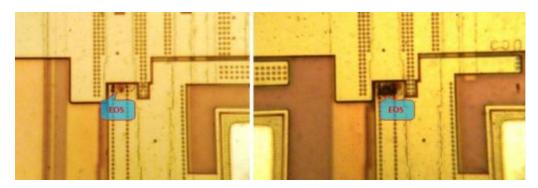

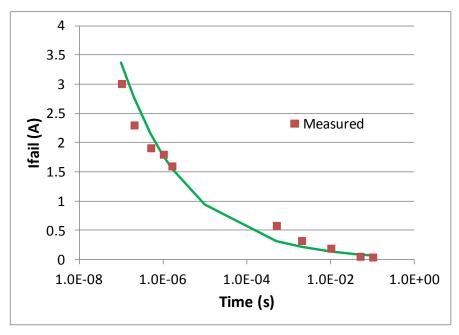

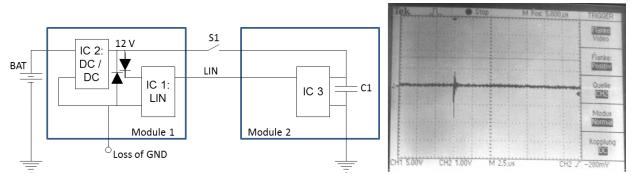

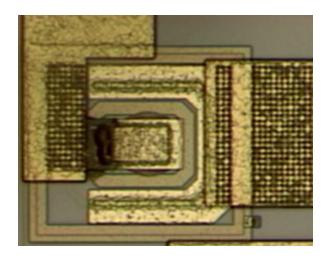

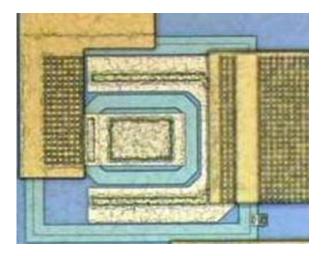

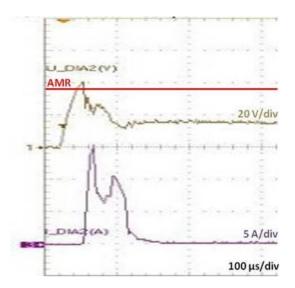

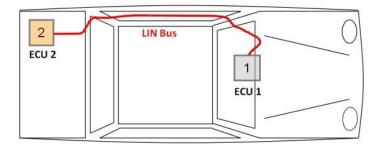

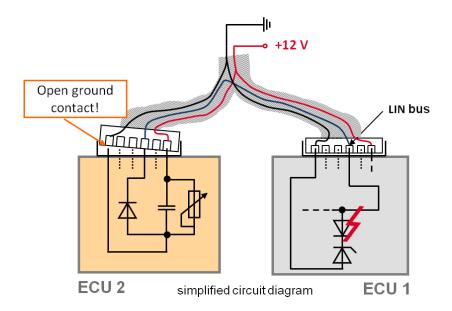

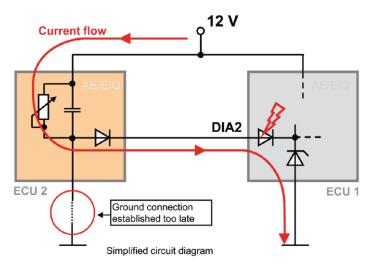

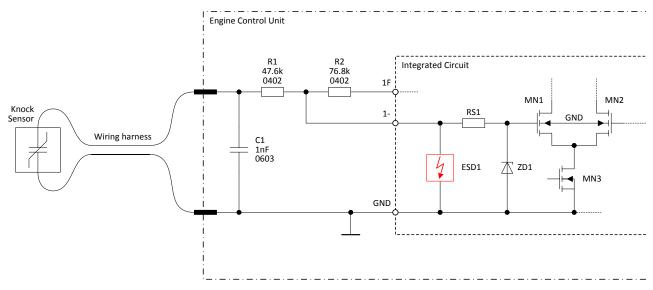

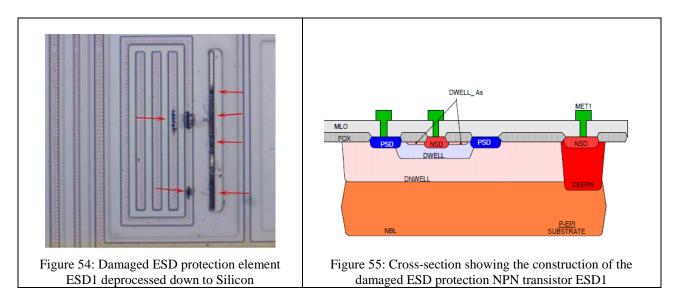

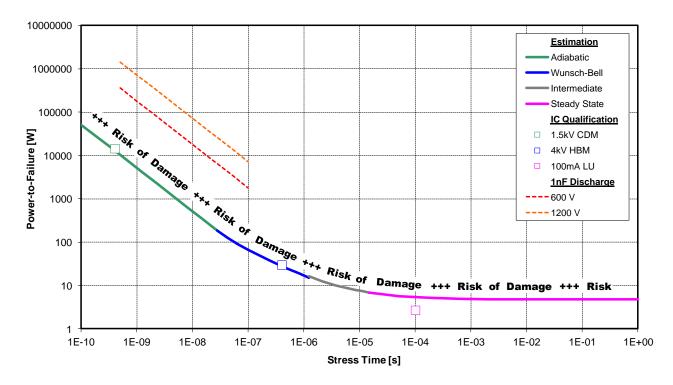

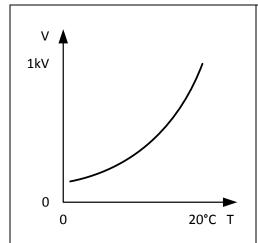

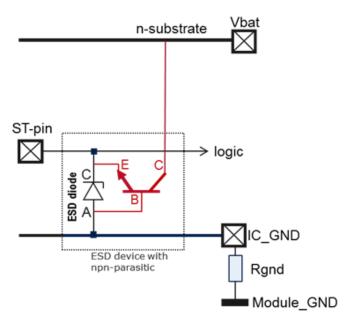

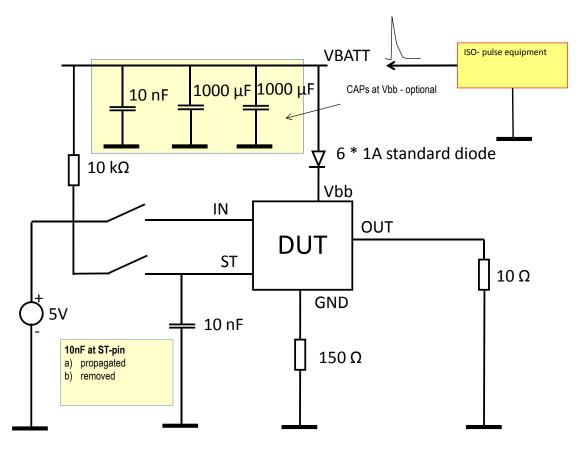

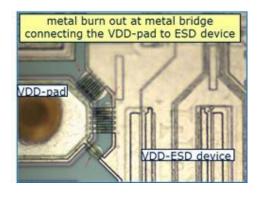

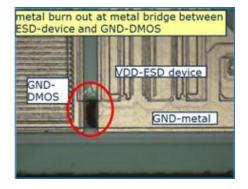

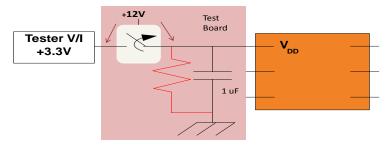

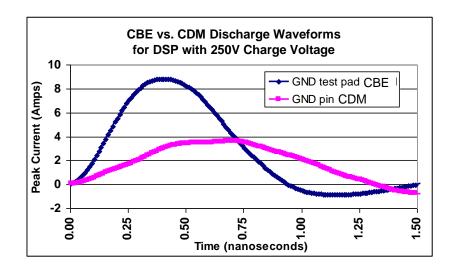

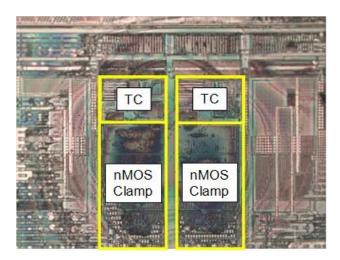

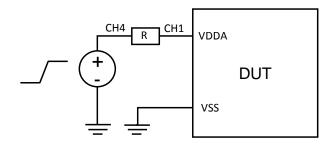

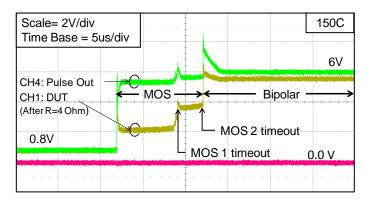

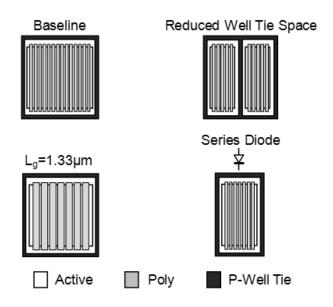

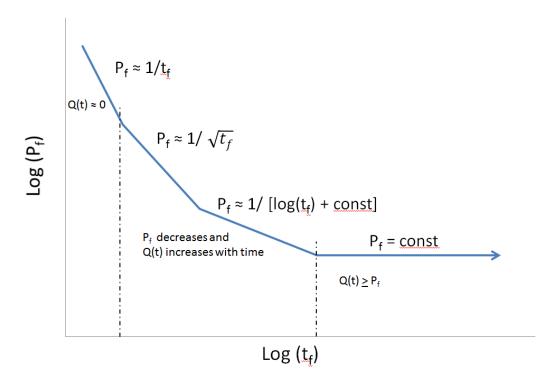

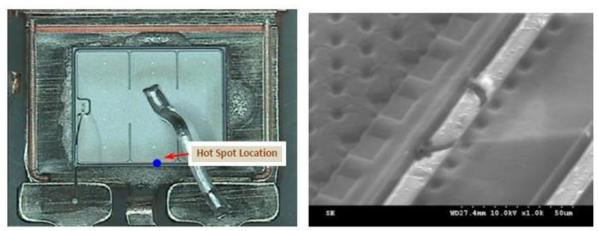

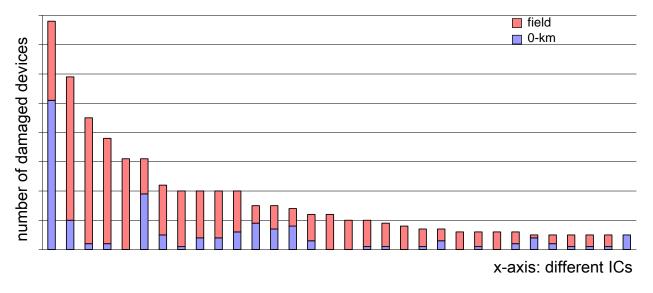

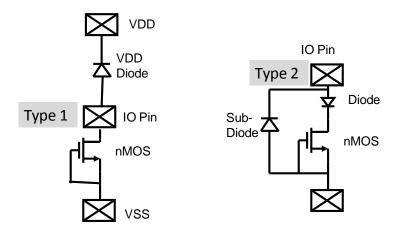

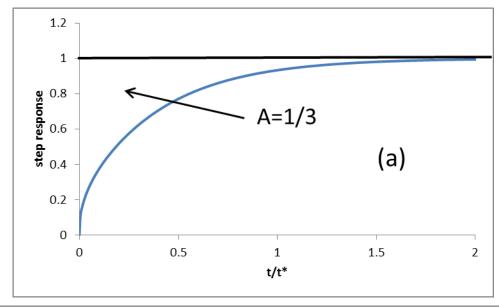

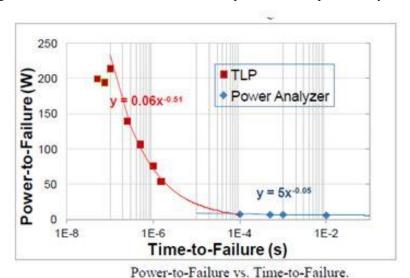

- [62] Yamaoto and Tsuru, "Time-Dependent Temperature Calculations of Aluminum Lines Applied with Electrical Overstress Pulses", Japan Journal of Applied Physics, July 1996, Vol. 35, Part 1, No. 7, pp. 3852-3857